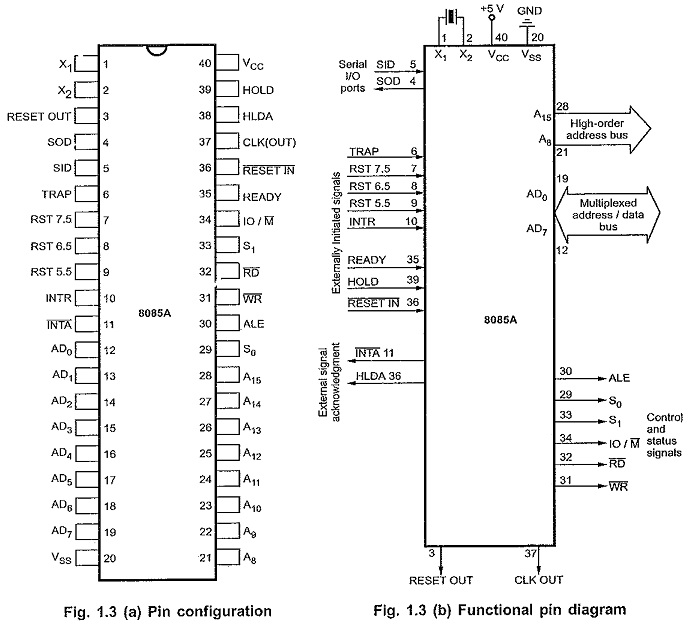

8085 Pin Diagram | Functional Pin Diagram of 8085 Microprocessor:

Fig. 1.3 (a) and (b) shows 8085 Pin Diagram and functional pin diagram of 8085 microprocessor respectively. The signals of 8085 Pin Diagram can be classified into seven groups according to their functions.

- Power supply and frequency signals.

- Data bus and address bus

- Control bus

- Interrupt signals

- Serial I/O signals

- DMA signals

- Reset signals

1. Power Supply and Frequency Signals:

- Vcc : It requires a single +5 V power supply.

- Vss : Ground reference.

- X1 and X2 : A tuned circuit like LC, RC or crystal is connected at these two The internal clock generator divides oscillator frequency by 2, therefore, to operate a system at 3 MHz, the crystal of tuned circuit must have a frequency of 6 MHz.

- CLK OUT : This signal is used as a system clock for other devices. Its frequency is half the oscillator frequency.

2. Data Bus and Address Bus:

A) AD0 to AD7 : The 8 bit data bus (D0 – D7) is multiplexed with the lower half (A0 – A7) of the 16 bit address bus. During first part of the machine cycle (T1), lower 8 bits of memory address or I/O address appear on the bus. During remaining part of the machine cycle (T2 and T3) these lines are used as a bi-directional data bus.

B) A8 to A15 : The upper half of the 16 bit address appears on the address lines A8 to A15. These lines are exclusively used for the most significant 8 bits of the 16 bit address lines.

3. Control and Status Signals:

A) ALE (Address Latch Enable) : We, know that AD0 to AD7 lines are multiplexed and the lower half of address (A0 – A7) is available only during T1 of the machine cycle. This lower half of address is also necessary during T2 and T3 of machine cycle to access specific location in memory or I/O port. This means that the lower half of an address must be latched in T1 of the machine cycle, so that it is available throughout the machine cycle. The latching of lower half of an address bus is done by using external latch and ALE signal from 8085 Pin Diagram.

B) RD and WR : These signals are basically used to control the direction of the data flow between processor and memory or I/O device/port. A low on RD indicates that the data must be read from the selected memory location or I/O port via data bus. A low on WR indicates that the data must be written into the selected memory location or I/O port via data bus.

C) IO/M, S0 and S1 : IO/M indicates whether I/O operation or memory operation is being carried out. S1 and S0 indicate the type of machine cycle in progress.

D) READY : It is used by the microprocessor to sense whether a peripheral is ready or not for data transfer. If not, the processor waits. It is thus used to synchronize slower peripherals to the microprocessor.

4. Interrupt Signals:

The 8085 Pin Diagram has five hardware interrupt signals : RST 5.5, RST 6.5, RST 7.5, TRAP and INTR. The microprocessor recognises interrupt requests on these lines at the end of the current instruction execution.

The INTA (Interrupt Acknowledge) signal is used to indicate that the processor has acknowledged an INTR interrupt.

5. Serial I/O Signals:

A) SID (Serial I/P Data) : This input signal is used to accept serial data bit by bit from the external device.

B) SOD (Serial O/P Data) : This is an output signal which enables the transmission of serial data bit by bit to the external device.

6. DMA Signal:

A) HOLD : This signal indicates that another master is requesting for the use of address bus, data bus and control bus.

B) HLDA : This active high signal is used to acknowledge HOLD request.

7. Reset Signals:

A) RESET IN : A low on this pin

- Sets the program counter to zero (0000H).

- Resets the interrupt enable and HLDA flip-flops.

- Tri-states the data bus, address bus and control bus. (Note : Only during RESET is active).

- Affects the contents of processor’s internal registers randomly.

On reset, the PC sets to 0000H which causes the 8085 Pin Diagram to execute the first instruction from address 0000H. For proper reset operation reset signal must be held low for at least 3 clock cycles. The power-on reset circuit can be used to ensure execution of first instruction from address 0000H.

B) RESET OUT : This active high signal indicates that processor is being reset. This signal is synchronized to the processor clock and it can be used to reset other devices connected in the system.