Machine Cycle in 8085 Microprocessor:

The seven Machine Cycle in 8085 Microprocessor are :

- Opcode Fetch Cycle

- Memory Read

- Memory Write

- I/O Read

- I/O Write

- Interrupt Acknowledge

- Bus Idle

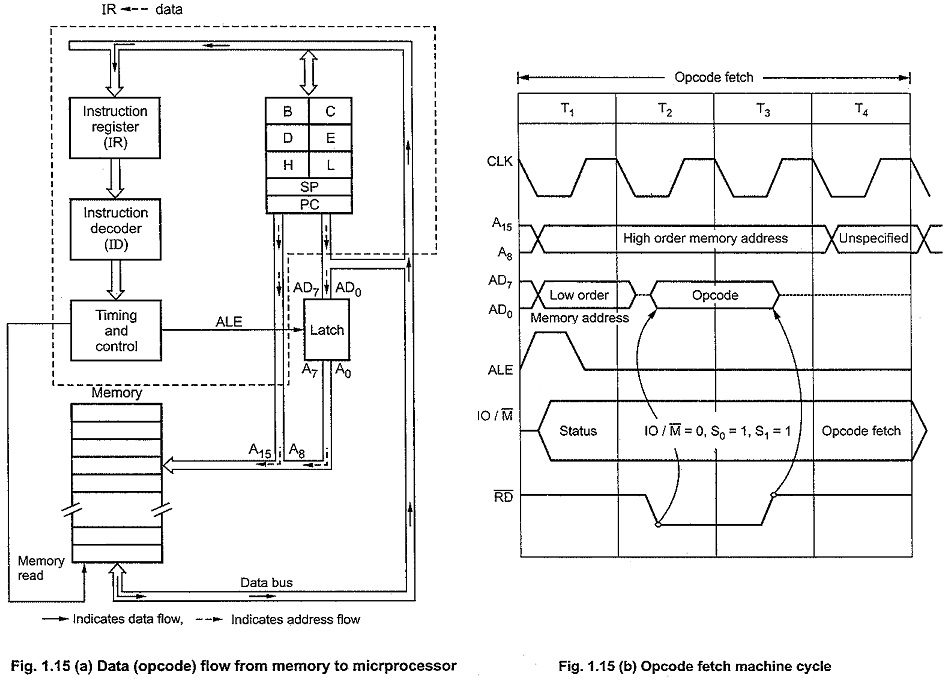

1. Opcode Fetch Cycle:

The first Machine Cycle of 8085 Microprocessor of every instruction is opcode fetch cycle in which the 8085 finds the nature of the instruction to be executed. In this Machine Cycle in 8085, processor places the contents of the Program Counter on the address lines, and through the read process, reads the opcode of the instruction. Fig. 1.15 (a) shows flow of data (opcode) from memory to the microprocessor and Fig. 1.15 (b) shows the timing diagram for Opcode Fetch Machine Cycle 8085. The length of this cycle is not fixed. It varies from 4T states to 6T states as per the instruction. The following section describes the opcode fetch cycle in step by step manner.

Step 1 : (State T1) In T1 state, the 8085 places the contents of program counter on the address bus. The high-order byte of the PC is placed on the A8 – A15 lines. The low-order byte of the PC is placed on the AD0 – AD7 lines which stays on only during T1. Thus microprocessor activates ALE (Address Latch Enable) which is used to latch the low-order byte of the address in external latch before it disappears.

In T1, 8085 also sends status signals IO/M, S1, and S0. IO/M specifies whether it is a memory or I/O operation, S1 status specifies whether it is read/write operation; S1 and S0 together indicates read, write, opcode fetch, machine cycle operation, or whether it is in HALT state. In opcode fetch machine cycle status signals are : IO/M = 0, S1 = 1, S0 = 1.

Step 2 : (State T2) In T2, low-order address disappears from the AD0 – AD7 lines. (However A0 – A7 remain available as they were latched during T1). In T2, 8085 sends RD signal low to enable the addressed memory location. The memory device then places the contents of addressed memory location on the data bus (AD0 – AD7).

Step 3 : (State T3) During T3, 8085 loads the data from the data bus in its Instruction Register and raises RD to high which disables the memory device.

Step 4 : (State T4) In T4, microprocessor decodes the opcode, and on the basis of the instruction received, it decides whether to enter state T5 or to enter state T1 of the next Machine Cycle of 8085 Microprocessor. One byte instructions those operate on eight bit data (8 bit operand) are executed in T4.

For example : MOV A, B, ANA D, ADD B, INR L, DCR C, RAL and many more.

Note : For one byte instructions which operate on eight bit data, data is always available in the internal memory of 8085 i.e. registers.

Step 5 : (State T5 and T6) State T5 and T6, when entered, are used for internal microprocessor operations required by the instruction. During T5 and T6 , 8085 performs stack write, internal 16 bit; and conditional return operations depending upon the type of instruction. One byte instructions those operate on sixteen bit data (16 bit operand) are executed in T5 and T6. For example DCX H, PCHL, SPHL, INX H, etc.

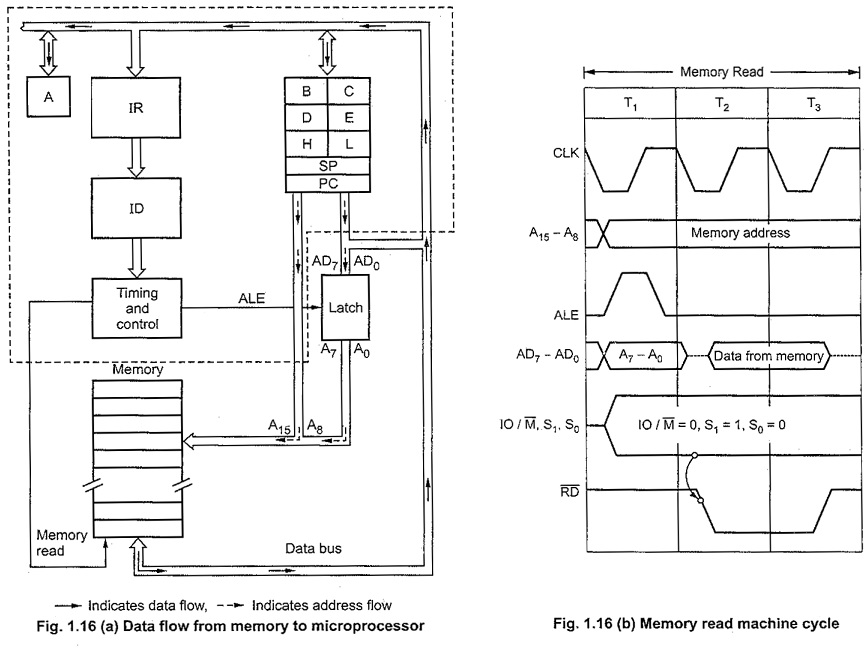

2.Memory Read Cycle:

The 8085 executes the memory read cycle to read the contents of R/W memory or ROM. The length of this machine cycle is 3-T states (T1 – T3). In this Machine Cycle in 8085, processor places the address on the address lines from the stack pointer, general purpose register pair or program counter, and through the read process, reads the data from the addressed memory location. Fig. 1.16 (a) shows flow of data from memory to the microprocessor and Fig. 1.16 (b) shows the timing diagram for memory read machine cycle. Memory read machine cycle is similar to the opcode fetch machine cycle. However, they use only states T1 to T3, and the status signal values (IO/M = 0, S1 = 1, S0 = 0) appropriate for memory read machine cycle are issued in T1.

The following section describes the memory read machine cycle in step by step manner.

Step 1 : (State T1) In T1 state, microprocessor places the address on the address lines from stack pointer, general purpose register pair or program counter and activates ALE signal in order to latch low-order byte of address.

During T1, 8085 sends status signals : IO/M = 0, S1 = 1, and S0 = 0 for memory read machine cycle.

Step 2 : (State T2) In T2, 8085 sends RD signal low to enable the addressed memory location. The memory device then places the contents of addressed memory location on the data bus (AD0 -AD7).

Step 3 : (State T3) During T3, 8085 loads the data from the data bus into specified register (F, A, B, C, D, E, H, and L) and raises RD to high which disables the memory device.

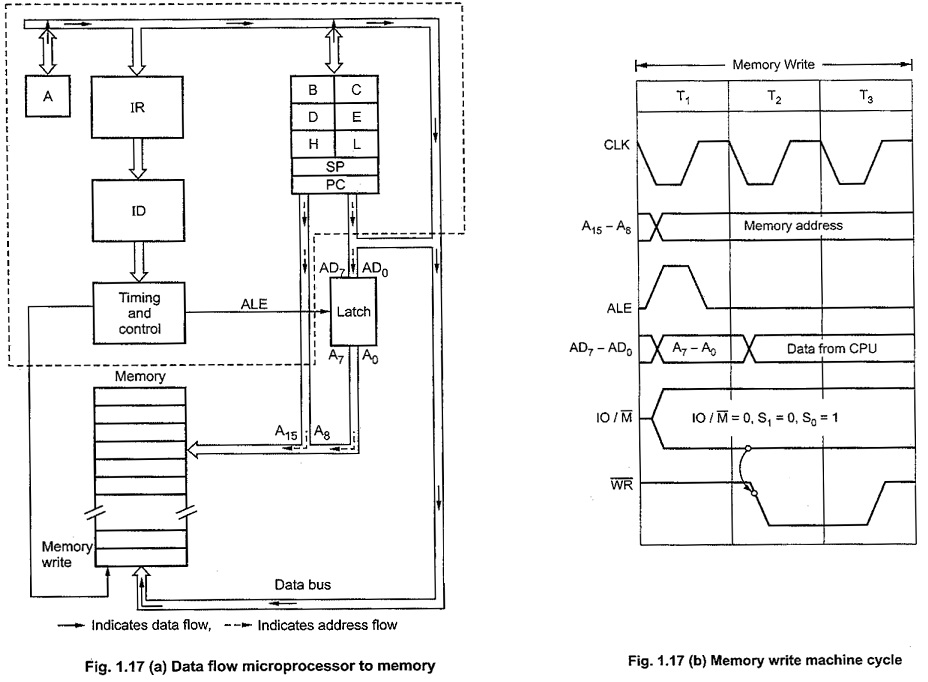

3.Memory Write Cycle:

The 8085 executes the memory write cycle to store the data into data memory or stack memory. The length of this machine cycle is 3T states. (T1 – T3). In this Machine Cycle of 8085 Microprocessor, processor places the address on the address lines from the stack pointer or general purpose register pair and through the write process, stores the data into the addressed memory location. Fig. 1.17 shows the timing diagram for memory write machine cycle. The memory write timing diagram is similar to the memory read timing diagram, except that instead of RD, WR signal goes low during T2 and T3. The status signals for memory write cycle are : IO/M = 0, S1 = 0, S0 = 1. The following section describes the memory write machine cycle in step by step manner.

Step 1 : (State T1) In T1 state, the 8085 places the address on the address lines from stack pointer or general purpose register pair and activates ALE signal in order to latch low-order byte of address. During T1, 8085 sends status signals :

IO/M = 0, S1 = 0 and S0 = 1 for memory write machine cycle.

Step 2 : (State T2) In T2, 8085 places data on the data bus and sends WR signal low for writing into the addressed memory location.

Step 3 : (State T3) During T3, WR signal goes high, which disables the memory device and terminates the write operation.

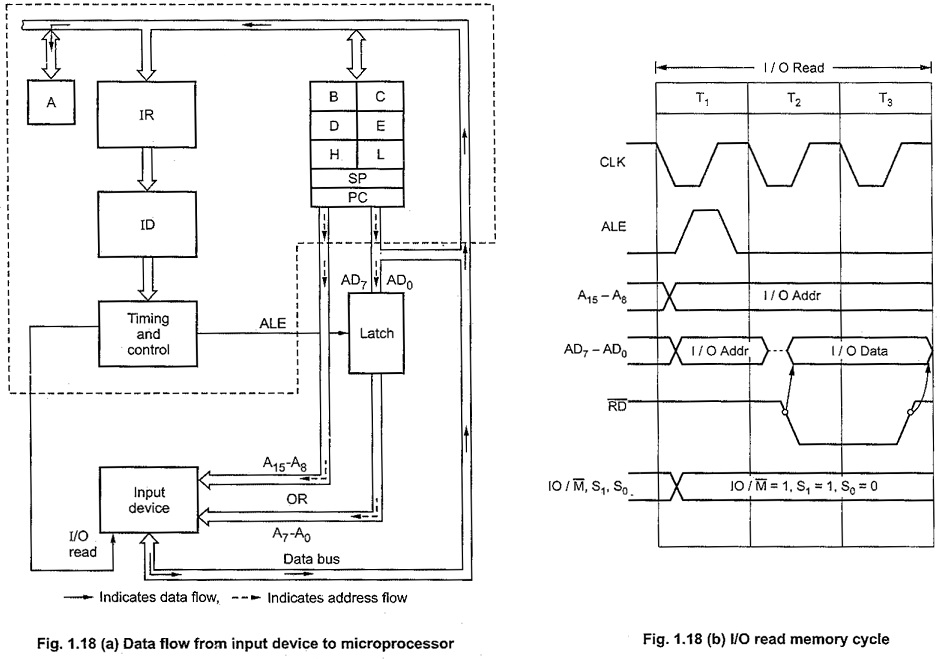

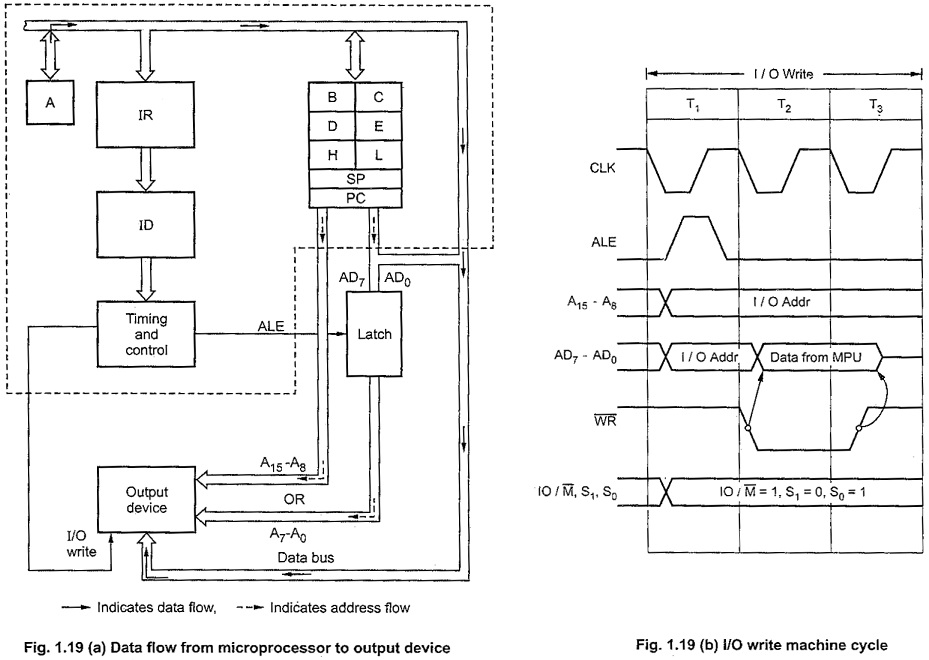

4, 5. I/O Read and I/O Write cycles:

The I/O read and I/O write machine cycles are similar to the memory read and memory write machine cycles, respectively, except that the 10/M signal is high for I/O read and I/O write machine cycles. High IO/M signal indicates that it is an I/O operation. Fig. 1.18 (b) and Fig. 1.19 (b) show the timing diagrams for I/O read and I/O write cycles, respectively.

6. Interrupt Acknowledge Cycle:

In response to INTR signal, 8085 executes interrupt acknowledge machine cycle to read an instruction from the external device. Theoretically, the external device can place any instruction on the data bus in response to INTA. However, only RST and CALL, save the PC contents (return address) before transferring control to the interrupt service routine. The next sections explain Interrupt Acknowledge Cycle of 8085 for RST and CALL instructions.

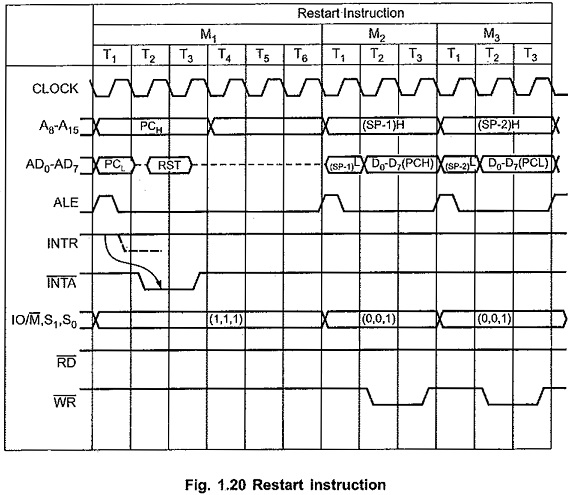

Interrupt Acknowledge Cycle for RST instruction:

Fig. 1.20 shows the timing diagram of the interrupt acknowledge machine cycle and execution of RST instruction. The interrupt acknowledge cycle is similar to the opcode fetch cycle, with two exceptions.

- The INTA signal is activated instead of the RD signal.

- The status lines (IO/M, S0 and S1) are 111 instead of 011:

During interrupt acknowledge machine cycle (M1), the RST is decoded, which initiates 1 byte CALL instruction to the specific vector location. The machine cycles M2 and M3 are memory write cycles that store the contents of the program counter on the stack, and then a new instruction cycle begins.

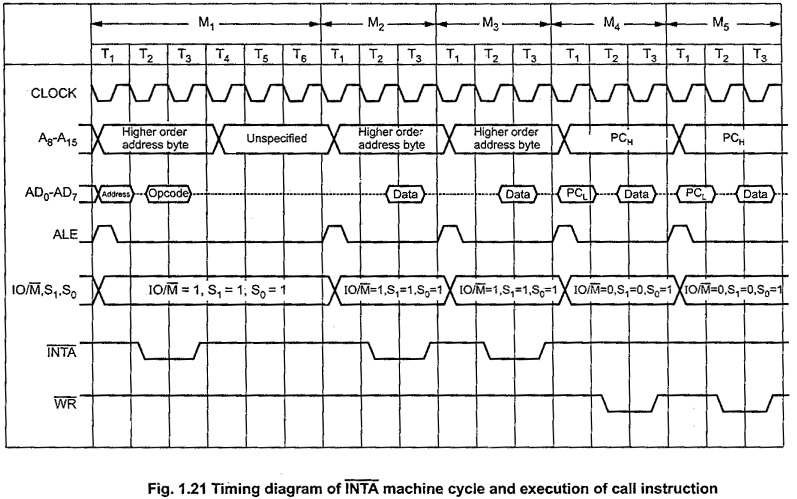

Interrupt Acknowledge Cycle for CALL instruction:

Fig. 1.21 shows the timing diagram of the Interrupt Acknowledge Cycle of 8085 and execution of a CALL instruction. For CALL instruction, it is necessary to fetch the two bytes of the CALL address through two additional interrupt acknowledge machine cycles (M2 and M3 in the 1.21). The machine cycles M4 and M5 are memory write cycles that store the contents of the program counter on the stack, and then a new instruction cycle begins.

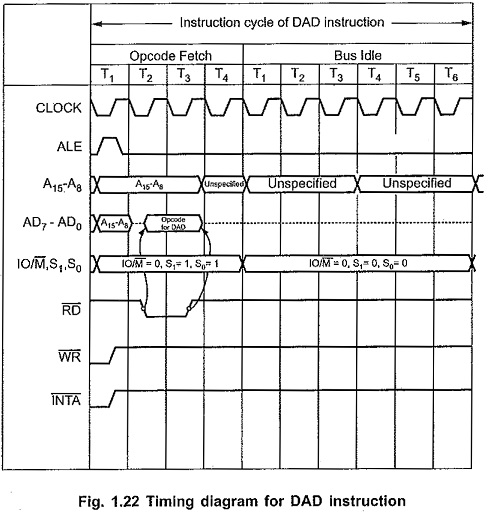

7. Bus Idle Cycle:

There are few situations where the machine cycles are neither Read nor Write. These situations are:

1.For execution of DAD instruction (this instruction adds the contents of a specified register pair to the contents of HL register pair) ten T states are required. This means that after execution of opcode fetch machine cycle, DAD instruction requires 6 extra T-states to add 16 bit contents of a specified register pair to the contents of HL register pair. These extra T-states which are divided into two machine cycles do not involve any memory or I/O operation. These Machine Cycle in 8085 are called BUS IDLE machine cycles. Fig. 1.22 shows Bus Idle Machine Cycle of 8085 Microprocessor for DAD instruction.

In the case of DAD, these Bus Idle cycles are similar to memory read cycles, except RD and ALE signals are not activated.

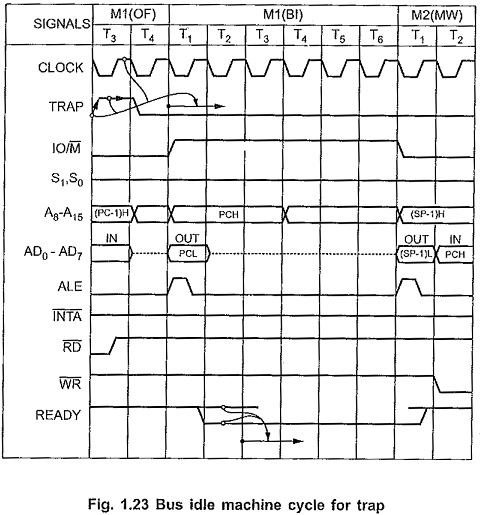

2.During internal opcode generations, for TRAP and RST interrupts, 8085 executes Bus Idle Machine Cycles. Fig. 1.23 shows the Bus Idle Machine Cycle of 8085 Microprocessor for TRAP. In response to TRAP interrupt, 8085 enters into a Bus Idle Machine Cycle during which it invokes restart instruction, stores the contents of PC onto the stack and places 0024H (Vector address of TRAP) onto_ the program counter.

The number of machine cycles required to fetch complete instruction depends on the instruction type :

- One byte 2. Two byte or 3. Three byte

One byte instruction doesn’t require any additional machine cycle. Two byte instruction requires one additional memory read machine cycle, whereas three byte instruction requires two additional memory read machine cycles.

The number of Machine Cycle in 8085 required to execute the instruction depends on the particular instruction. The total number of machine cycles required varies from one to five. It is possible that memory read and memory write machine cycles occur more than once in a single instruction cycle. The following examples illustrate the timing diagrams and machine cycles used for few 8085 instructions.

Concept of Wait States in 8085:

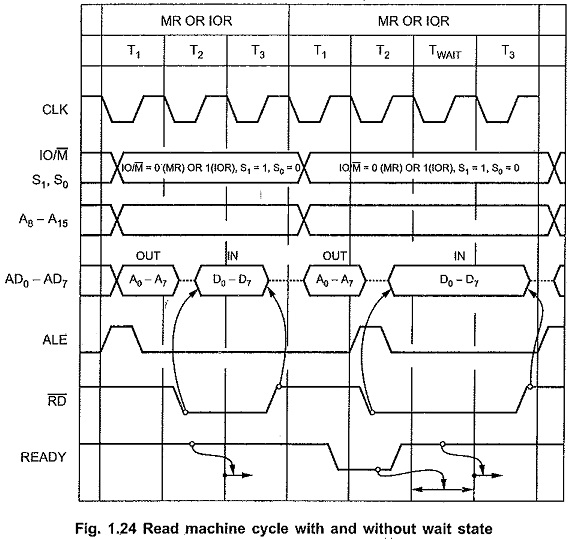

In some applications, speed of memory system and I/O system are not compatible with the microprocessor’s timings. This means that they take longer time to read/write data. in such situations, the microprocessor has to confirm whether a peripheral is ready to transfer data or not. If READY pin is high, the peripheral is ready otherwise 8085 enters wait state.

Fig. 1.24 shows the timing diagram for memory read machine cycle with and without wait state.

Concept of Wait States in 8085 continue to be inserted as long as READY is low. After the wait state, 8085 continues with T3 of the machine cycle. During a wait state the contents of the address bus, the data bus, and the control bus are all held constant.

The wait state then gives an addressed memory or I/O port an extra clock cycle time to output valid data on the data bus. This feature allows to use cheaper memory or I/O devices that have longer access times.