Programmable Array Logic (PAL):

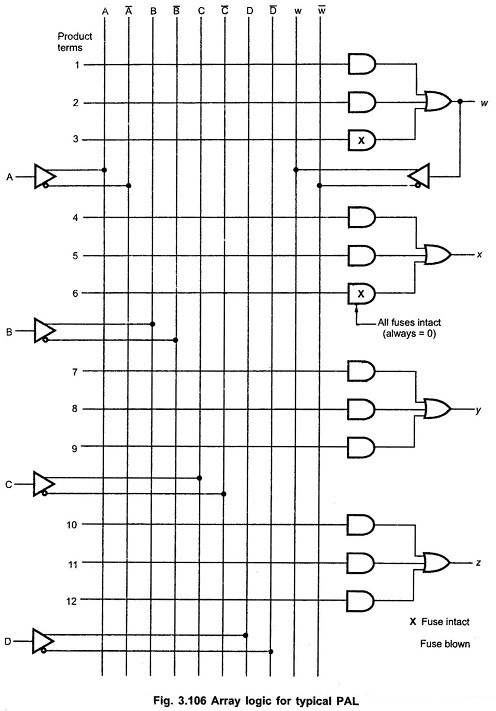

We have seen that PLA device with a Programmable AND array and Programmable OR array. However, Programmable Array Logic (PAL) is a programmable logic device with a fixed OR array and a programmable AND array. Because only AND gates are programmable , the PAL is easier to program, but is not as flexible as the PLA. Fig.3.106 shows the array logic of a typical PAL.

It has four inputs and four outputs. Each input has buffer and an inverter gate. It is important to note that two gates are shown with one composite graphic symbol with normal and complement outputs.

There are four sections. Each section has three programmable AND gates and one fixed OR gate. The output of section 1 is connected to a buffer-inverter gate and then fedback into the inputs of the AND gates, through fuses. This allows the logic designer to feed an output function back as an input variable to create a new function. Such PALs are referred to as Programmable I/O PALs.

A typical PAL integrated circuit may have eight inputs, eight outputs, and eight sections, each consisting of an eight wide AND-OR array.