Intel 8096 CPU Structure:

The major components of the CPU on the 8096BH are the register file and the register ALU (RALU). The Intel 8096 CPU Structure consists of a 16-bit ALU. It operates on a 256 byte register file instead of an accumulator. Hence it is called Register ALU or RALU.

CPU Register File:

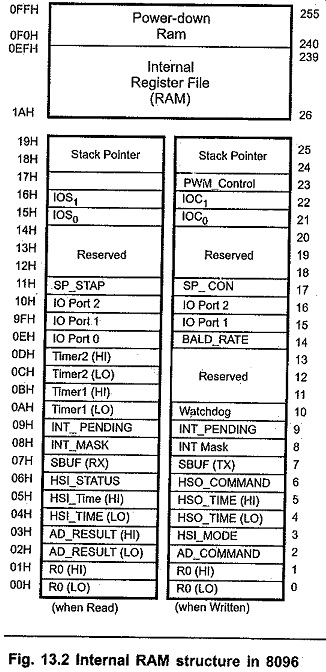

The Fig. 13.2 shows the memory map of a Intel 8096 CPU Structure register file. As mentioned earlier, the CPU register file has 256 bytes of memory. From locations OOH to FFH. No code can be executed from these CPU register file locations. If an attempt is made to execute instructions from these locations, the instructions will be automatically fetched from the external memory. Two 8-bit temporary registers provided by the CPU hardware are used to access the locations from the Intel 8096 CPU Structure register file.

Out of 256 locations, the first 24 memory locations OOH to 1714 are the special function registers (SFRs). The special function registers are used to control the on-chip I/O section. The remaining 232 locations are the RAM locations. These locations can be accessed as bytes, words, or double words. Since each of these locations can be used by the RALU, there are essentially 232 accumulators. The first word in the RAM (locations 18H and 19H) is a stack pointer. It cannot be used for data when stack manipulations are taking place. The stack pointer must be initialized by the user program and can point anywhere in the 64 Kbyte (External) memory space. The upper 16 bytes (FOH through FFH) of RAM is called Power down RAM because these locations receive their power from the VPD pin in the power down mode. Hence in the power down only these locations are alive.

Special Function Registers:

SFRs control the on-chip I/O section and as mentioned earlier it consi its of 24 registers. Many of these registers serve two functions; one if they are read from, the other if they are written to. Fig. 13.2 shows the locations and names of these registers.

Several registers within the SFR space are labelled as “RESERVED”. These registers are reserved for future expansion or test purposes. Reads or writes of these registers may produce unexpected results. For example, writing to location 000CH will set both timers to OFFFXH, this feature is for use in testing the part and should not be used in programs.

RALU:

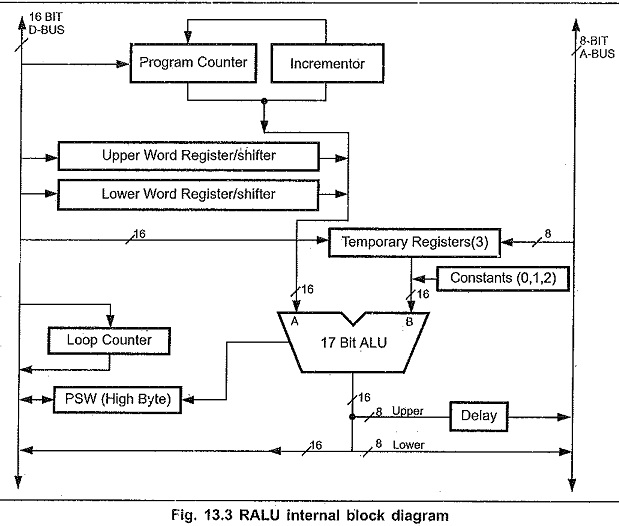

Instructions to the RALU are taken from the A-Bus and stored temporarily in the instruction register. The Control Unit decodes the instructions and generates the correct sequence of signals to have the RALU perform the desired function.

Fig. 13.3 shows the internal block diagram of RALU. It contains a 17-bit ALU, the program status word (PSW), It contains a 17-bit ALU, the Program Status Word (PSW), the Program Counter (PC), a loop counter, and three temporary registers. All of the registers are 16-bits or 17-bits (16 + sign extension) wide. Some of the registers have the ability to perform simple operations to off-load the ALU.

A separate increment is used for the PC; however, jumps must be handled through the ALU. Two temporary registers are used for the operations which require logical shifts including Normalize, Multiply, and Divide. The “Lower Word” register is used only when double word quantities are being shifted, the “Upper Word” register is used whenever a shift is performed or as a temporary register for many instructions. Loop Counter is used to count repetitive shifts. The third temporary register stores the second operand of two operand instructions. This includes the multiplier during multiplications and the divisor during divisions. To perform subtractions, one of the temporary registers can be complemented before being placed into the “B” input of the ALU.

Fig. 13.3 also shows the DELAY block. It is used to convert the 16-bit bus into an 8-bit bus. This is required as all addresses and instructions are carried on the 8-bit A bus. Several constants, such as. 0, 1 and 2 are stored in the RALU for use in speeding up certain calculations. These come in handy when the RALU needs to make a 2’s complement number or perform an increment or decrement instruction.