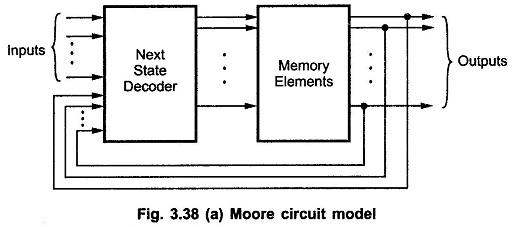

Synchronous Sequential Circuits

Synchronous Sequential Circuits or Clocked Sequential Circuits: In Synchronous Sequential Circuits or clocked sequential circuits, clocked flip-flops are used as memory elements, which change their individual states in synchronism with the periodic clock signal. Therefore,…