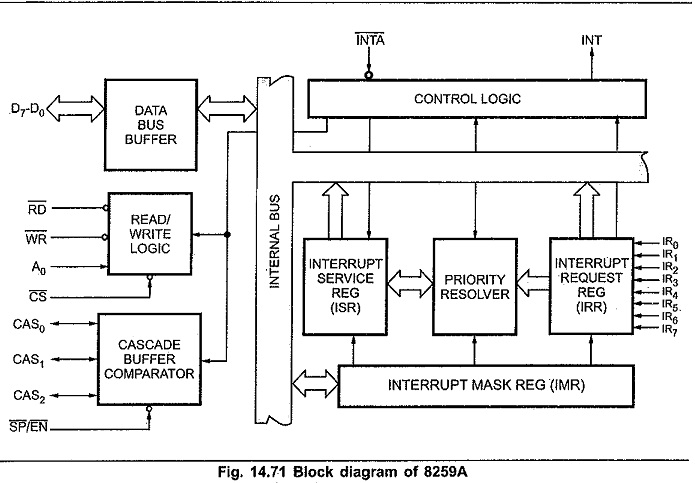

8259 Block Diagram:

Fig. 14.71 shows the internal 8259 Block Diagram. It includes eight blocks : data bus buffer, read/write logic, control logic, three registers (IRR, ISR and IMR), priority resolver, and cascade buffer.

Data Bus Buffer:

The data bus buffer allows the 8085 to send control words to the 8259A and read a status word from the 8259 Block Diagram. The 8-bit data bus buffer also allows the 8259A to send interrupt opcode and address of the interrupt service subroutine to the 8085.

Read/Write Logic:

The RD and WR inputs control the data flow on the data bus when the device is selected by asserting its chip select (CS) input low.

Control Logic:

This block has an input and an output line. If the 8259A is properly enabled, the interrupt request will cause the 8259A to assert its INT output pin high. If this pin is connected to the INTR pin of an 8085 and if the 8085 Interrupt Enable (IE) flag is set, then this high signal will cause the 8085 to respond INTR as explained earlier.

Interrupt Request Register (IRR):

The IRR is used to store all the interrupt levels which are requesting the service. The eight interrupt inputs set corresponding bits of the Interrupt Request Register upon service request.

Interrupt Service Register (ISR):

The Interrupt Service Register (ISR) stores all the levels that are currently being serviced.

Interrupt Mask Register (IMR):

Interrupt Mask Register (IMR) stores the masking bits of the interrupt lines to be masked. This register can be programmed by an Operation Command Word (OCW). An interrupt which is masked by software will not be recognised and serviced even if it sets the corresponding bits in the IRR.

Priority Resolver:

The priority resolver determines the priorities of the bits set in the IRR. The bit corresponding to the highest priority interrupt input is set in the ISR during the INTA input.

Cascade Buffer Comparator:

This section generates control signals necessary for cascade operations. It also generates Buffer-Enable signals. As stated earlier, the 8259 Block Diagram can be cascaded with other 8259s in order to expand the interrupt handling capacity to sixty-four levels. In such a case, the former is called a master, and the latter are called slaves. The 8259 can be set up as a master or a slave by the SP/EN pin.

CAS0— CAS2

For a master 8259, the CAS0-CAS2 pins are output pins, and for slave 8259, these are input pins. When the 8259 is a master (that is, when it accepts interrupt requests from other 8259s), the CALL opcode is generated by the Master in response to the first INTA. The vector address must be released by the slave 8259. The master sends an identification code of three-bits to select one out of the eight possible slave 8259s on the CAS0-CAS2 lines. The slave 8259s accept these three signals as inputs (on their CAS0 – CAS2 pins) and compare the code sent by the master with the codes assigned to them during initialization. The slave thus selected (which had originally placed an interrupt request to the master 8259) then puts the address of the interrupt service routine during the second and third INTA pulses from the CPU.

SP / EN (Slave Program /Enable Buffer):

The SP/EN signal is tied high for the master. However it is grounded for the slave.

In large systems where buffers are used to drive the data bus, the data sent by the 8259 in response to INTA cannot be accessed by the CPU (due to the data bus buffer being disabled). If an 8259 is used in the buffered mode (buffered or non-buffered modes of operation can be specified at the time of initializing the 8259), the SP/EN pin is used as an output which can be used to enable the system data bus buffer whenever the data bus outputs of 8259 are enabled (i.e. when it is ready to send data).

Thus, in non-buffered mode, the SP/EN pin of an 8259 is used to specify whether the 8259 is to operate as a master or as a slave, and in the buffered mode, the SP/EN pin is used as an output to enable the data bus buffer of the system.

Interrupt Sequence:

The events occur as follows in an 8085 system :

- One or more of the INTERRUPT REQUEST lines (IR0-IR7) are raised high, setting the, corresponding IRR bit(s).

- The priority resolver checks three registers : The IRR for interrupt requests, the IMR for masking bits, and the ISR for the interrupt request being served. It resolves the priority and sets the INT high when it is appropriate to do so. •

- In response to the INTR signal, 8085 completes current instruction cycle and executes interrupt acknowledge cycle, thus giving an INTA pulse.

- Upon receiving an INTA from the 8085, the highest priority ISR bit is set and the corresponding IRR bit is reset. Then 8259A places the opcode for CALL instruction on the data bus.

- This CALL instruction initiates two more interrupt acknowledge cycles.

- These two interrupt acknowledge cycles allow the 8259 to release preprogrammed subroutine address onto, the data bus. In response to second interrupt acknowledge pulse 8259 place’s a lower byte of interrupt subroutine address and in response to third interrupt acknowledge pulse 8259 places a higher byte of the subroutine address.

- This completes the interrupt cycle. In the AE01 (Automatic End of Interrupt) mode the ISR bit is reset at the end of the second INTA pulse. Otherwise, the ISR bit remains set until the issue of an appropriate EOI command at the end of the interrupt subroutine.

Operating Modes of 8259 and Features of 8259 Microprocessor:

The various Operating Modes of 8259 Programmable Interrupt Controller are :

- Fully Nested Mode of 8259,

- Special Fully Nested Mode in 8259 (SFNM)

- Rotating Priority Mode of 8259,

- Special Mask Mode in 8259, and

- Polled Mode in 8259.

1. Fully Nested Mode of 8259 (FNM) :

After initialization, the 8259A operates in fully nested mode so it is called default mode. The 8259 continues to operate in the Fully Nested Mode until the mode is changed through Operation Command Words. In this mode, IR0 has highest priority and IR7 has lowest priority. When the interrupt is acknowledged, it sets the corresponding bit in ISR. This bit will inhibit all interrupts of the same or lower level, however it will accept higher priority interrupt requests. The vector address corresponding to this interrupt is then sent. The bit in the ISR will remain set until an EOI command is issued by the microprocessor at the end of interrupt service routine. But if AEOI (Automatic End Of Interrupt) bit is set, the bit in the ISR resets at the trailing edge of the last INTA .

End of Interrupt (EOI):

- The ISR bit can be reset by an End of Interrupt command issued by the CPU, usually just before exiting from the interrupt routine.

- In the Fully Nested Mode, the highest level in the ISR would necessarily correspond to the last interrupt acknowledged and serviced. In such a case, a non-specific EOI command may be issued by the CPU.

- However, if the FNM is not used, the 8259 may not be able to determine the last interrupt acknowledged. In such a case, a specific EOI command will have to be issued by the CPU.

- It should be noted that in the cascade mode, the EOI command must be issued twice, once for the master and once for the slave.

Automatic End of Interrupt (AEOI):

If the AEOI mode is set, the 8259 Block Diagram will perform a non-specific EOI on its own on the trailing edge of The third INTA pulse. The AEOI mode can only be used for a master 8259 and not for a slave.

2. Special Fully Nested Mode in 8259 (SFNM):

In the FNM, on the acknowledgement of an interrupt, further interrupts from the same level are disabled. Consider a large system which uses cascaded 8259s and where the interrupt levels within each slave have to be considered. An interrupt request input to a slave, in turn causes the slave to place an interrupt request to the master on one of the master’s inputs. Further interrupts to the slave will cause the slave to place requests to the master on the same input to the master, but these will not be recognised because further interrupts on the same input level are disabled by the master.

The Special Fully Nested Mode (SFNM) is used to avoid this problem. The SFNM is set up by ICW4 during initialisation. It is similar to the FNM except for the following differences:

- When an interrupt request from a slave is being serviced, the slave is allowed to place further requests if these requests are of a higher priority than the request currently being serviced. These interrupts are recognised by the master and it initiates interrupt requests to the CPU.

- Before exiting from the interrupt service routine, a non-specific EOI must be sent to the slave and its ISR must be read to determine if it was the only interrupt to the slave. If the ISR is empty, a non-specific EOI command can be sent to the master. If it is not empty, it implies that the same IR level input to the master is to be serviced again due to snore than one interrupts being presented to the slave, and an EOI must not be sent to the master.

3. Rotating Priority Mode of 8259:

The Rotating Priority mode can be set in (i) Automatic Rotation, and (ii) Specific Rotation.

i) Automatic Rotation:

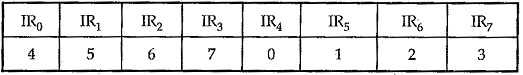

In this mode, a device, after being serviced, receives the lowest priority. The device just been serviced, will receive the seventh priority. Here IR3 has just been serviced.

ii)Specific Rotation:

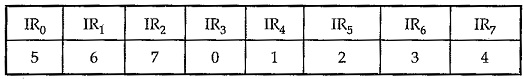

In the Automatic Rotation mode, the interrupt request last serviced is assigned the lowest priority, whereas in the Specific Rotation mode, the lowest priority can be assigned to any interrupt input (IR0 to IR7) thus fixes all other priorities.

For example if the lowest priority is assigned to IR2, other priorities are as shown below.

4. Special Mask Mode in 8259:

If any interrupt is in service, then the corresponding bit is set in ISR and the lower priority interrupts are inhibited. Some applications may require an interrupt service routine to dynamically alter the system priority structure during its execution under software control. For example, the routine may wish to inhibit lower priority requests for a portion of its execution but enable some of them for another portion. In these cases, we have to go for special mask mode. In the special mask mode it inhibits further interrupts at that level and enables interrupts from all other levels (lower as well as higher) that are not masked. Thus any interrupt may be selectively enabled by loading the mask register.

5. Polled Mode in 8259:

In this mode the INT output is not used. The microprocessor checks the status of interrupt requests by issuing poll command. The microprocessor reads contents of 8259A after issuing poll command. During this read operation the 8259A provides polled word and sets ISR bit of highest priority active interrupt request FORMAT.

I = 1 —> One or more interrupt requests activated.

I = 0 —> No interrupt request activated.

W2 W1 W0 —> Binary code of highest priority active interrupt request.