Instruction Set of 80386 Microprocessor:

The 80386 processor can support all the instructions of 80286. Usually, the instruction sets of 80286 are designed to operate with 8-bit or 16-bit data, but the same mnemonics may be executed with 8-bit, 16-bit, and 32-bit operands in the 80386 processor. Due to the enhanced architecture of 80386 over 80286, with additional general-purpose registers, segment registers and flag register, some new instructions were incorporated in the instruction set of 80286, to get the instruction set of 80386. As scaled addressing mode is added with 80386 processor, the number of Instruction Set of 80386 increased significantly. The newly added instructions can be divided into the following functional groups as given below:

- Bit scan instructions

- Bit test instructions

- Conditional set byte instructions

- Shift double instructions

- Control transfer via gates instructions

Bit-Scan Instructions The 80386 processor has two bit-scan instructions such as BSF (Bit-Scan Forward) and BSR (Bit-Scan Reverse). The BSF and BSR instructions can scan the operand for a ‘1’ bit, without rotating the operand. The BSF instruction scans the operand from right to left whereas the BSR instruction scans the operand from left to right. When a ‘1’ is encountered during the scan, a zero flag will be set and the bit position of ‘1’ will be stored into the destination operand. If there is no ‘1’, zero flag is reset.

Bit-Test Instructions The 80386 CPU has four bit-test instructions, namely, BT (Test a Bit), BTC (Test a Bit and Complement), BTS (Test and Set a Bit) and BTR (Test and Reset a Bit). The BT, BTC, BTS and BTR instructions test the bit position in the destination operand which is specified by the source operand. The carry flag is affected whenever the bit position of the destination operand satisfies the condition specified in the mnemonics. If the bit position in the destination operand, specified by the source operand is ‘1’ for BT instruction, the carry flag is set, or else the carry flag is cleared.

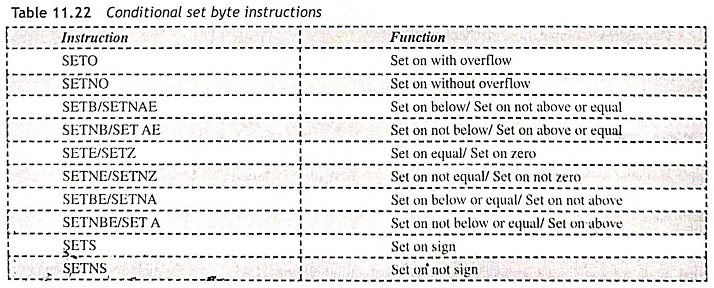

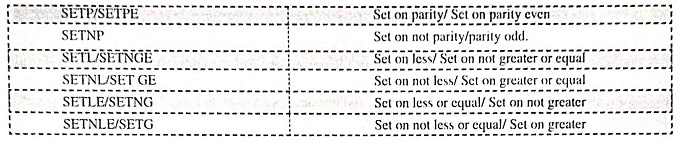

Conditional Set Byte Instructions The conditional set byte instructions can set all the operand bits when the condition specified by the instruction is true. There are 16 conditional set byte instructions as given in Table 11.22.

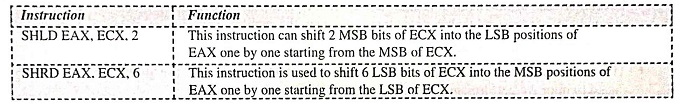

Shift Double Instructions The shift double instructions shift the specified number of bits from the source operand into the destination operand. The 80386 has two shift double instructions such as SHLD (Shift Left Double) and SHRD (Shift Right Double). The SHLD instruction is used to shift the number of bits specified in the instruction from the upper side. The SHRD instruction is used to shift the number of bits specified in the instruction from the lower side. For example,

Control Transfer Instructions The 80386 instruction set does not have any additional instructions for the intrasegment jump. However, for intersegrrient jumps, it has got a set of new instructions which are variations of the previous CALL and JUMP instructions, and are to be executed only in the protected mode. These instructions are used by 80386 to transfer the control either at the same privilege or at a different privilege level. Also, different versions of control transfer instructions are available to switch between the different task types and TSS (Task State Segment). The corresponding RET instructions are also available to switch back from the new task initiated via CALL, JMP or INT instructions to the parent task.