Features of 8259 Programmable Interrupt Controller:

The Features of 8259 Programmable Interrupt Controller are

1. It can manage eight priority interrupts. This is equivalent to providing eight interrupt pins on the processor in place of INTR pin.

2. It is possible to locate vector table for these additional interrupts any where in the memory map. However, all eight interrupts are spaced at the interval of either four or eight locations.

3. By cascading nine 8259s it is possible to get 64 priority interrupts.

4. Interrupt mask register makes it possible to mask individual interrupt request.

5. The Features of 8259A can be programmed to accept either the level triggered or the edge triggered interrupt request.

6. With the help of 8259A user can get the information .of pending interrupts, in-service interrupts and masked interrupts.

7. The Features of 8259A is designed to minimize the software and real time overhead in handling multi-level priority interrupts.

Features of 8259 Interrupts can be used for a variety of applications. Each of these interrupt applications requires a separate interrupt input. For 8085, we have five interrupt pins whereas 8086 has only one interrupt pin. For applications where processor interrupts are insufficient we have to use external device called a priority interrupt controller (PIC). By connecting such a device it is possible to increase the interrupt handling capacity of the microprocessor.

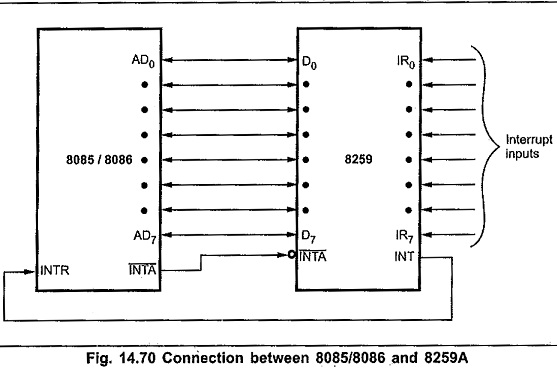

The Fig. 14.70 shows the connection between 8085/8086 and 8259A. The 8259A is a commonly used priority interrupt controller, which is specifically designed for use with interrupt signals INTR and INTA of Intel series. It is packaged in a 28 pin DIP. It uses NMOS technology and requires a single + 5V supply.